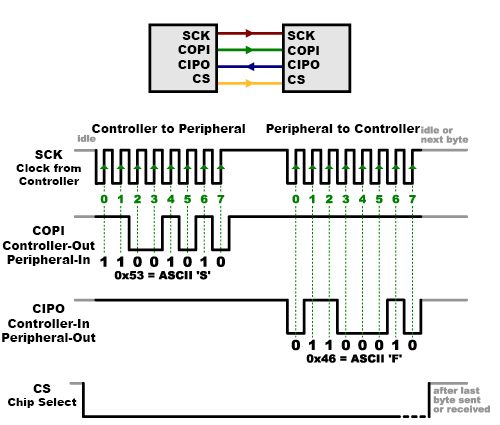

Transmission may continue for any number of clock cycles. If more data needs to be exchanged, the shift registers are reloaded and the process repeats. After the register bits have been shifted out and in, the master and slave have exchanged register values. On the next clock edge, at each receiver, the bit is sampled from the transmission line and set as a new least-significant bit of the shift register. On the clock edge, both master and slave shift out a bit and output it on the transmission line to the counterpart. Data is usually shifted out with the most significant bit (MSB) first. Transmissions normally involve two shift registers of eight bits (mostly but size varies based on the slaves), one in the master and one in the slave. This sequence is maintained even when only one-directional data transfer is intended. The master sends a bit on the MOSI pin and the slave reads it, while the slave sends a bit on the MISO pin and the master reads it. When multiple slaves are used, the master has to make the respective slave’s Slave select (SS/CS) pin LOW.ĭuring each SPI clock cycle, full-duplex data transmission occurs. Once the clock has been configured, then the master makes the Slave select (SS/CS) pin LOW that initiates the transfer. To begin communication, the bus master configures the clock, using a frequency supported by the slave device, typically up to a few MHz. SPI devices support much higher clock frequencies compared to I 2 C interfaces. So, as it is synchronized using the clock, it doesn’t have to wait for a response before doing other operations. The communication (data transmission between the master and the slave) is synchronized to the clock generated by the master. We will discuss that daisy chain later in this post. To avoid this scenario, they have introduced daisy chain logic. In I2C, the number of pins won’t increase even if you increase the slave devices. If you see the above picture, the master device has to use the 7 pins for 4 slave devices. You can easily understand this logic by using the below image. When you increase the number of slaves, then the Slave Select pin also increases. Note: on a slave-only device, MOSI may be labeled as SDI (Serial Data In) and MISO may be labeled as SDO (Serial Data Out). So, we can transmit and receive the data at the same time. SPI protocol is a Full-duplex as this protocol has separate pins for incoming data and outgoing data.

SS/CS/CE – Salve Select/Chip Select/Chip Enable.

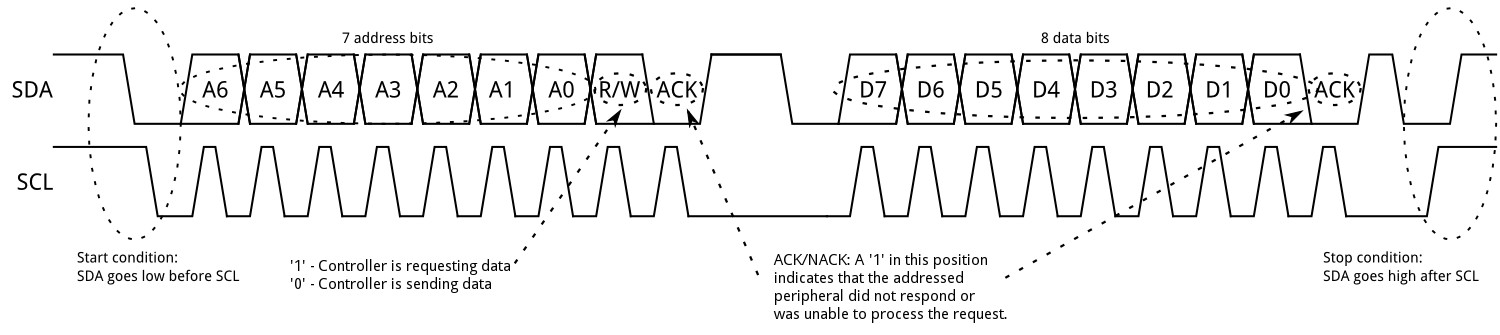

But some of the recent day devices support 3 pin mode and 4pin modes also. The maste r is p roviding the S PI clock an d the slave is re ceivi ng the SPI clock from the ma ster. But in I2C, we can have one or more master devices and one or more slave devices. SPI SpecificationĪn SPI – Serial Peripheral Interface protocol sy stem con sists of one m aste r devi ce a nd one o r mo re slave d evice s. The interface was developed by Motorola in the mid-1980s. Since it is synchronous communication, it uses a separate clock line and data lines. SPI – Serial Peripheral Interface is an interface bus commonly used to transmit and receive the data between microcontrollers and small peripherals such as shift registers, sensors, displays, flash memory, etc. SPI is one of the most popular serial communication protocols. We had discussed earlier about serial communication.